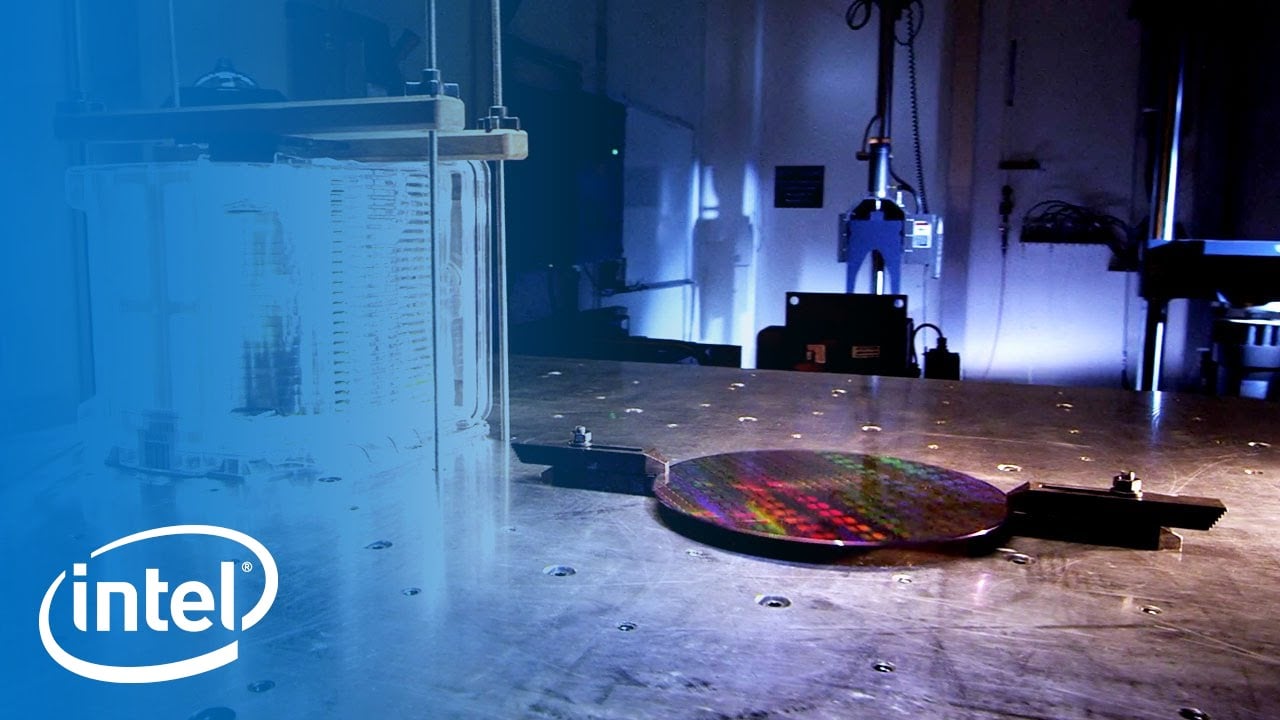

Intel, geleceğin eserlerinde kullanmak üzere 2nm altı üretim amaçlarına yönelik yeni bir transistör dizaynına odaklanıyor olabilir.

Yakın vakitte yayınlanan bir çevrimiçi patente bakılırsa şirket, Moore Yasasını “stacked forksheet transistors” olarak isimlendirdiği bir yaklaşım aracılığıyla canlı tutmak istiyor. Ekseriyetle olduğu üzere, patent bilinmeyen ve Intel PPA (Güç-Performans-Alan) iyileştirmeleri hakkında hiçbir argümanda bulunmuyor.

Mavi deve nazaran yeni transistör tasarımı günümüzün en gelişmiş üç kapılı dizaynlarına kıyasla daha fazla transistör sayısına müsaade veren 3B, dikey olarak istiflenmiş bir CMOS mimarisine dayanıyor. Öte taraftan transistörleri küçültmek çok sıkıntı hale gelmeye başlarken Intel’in patenti bile karşılaşılan zorlukları “overwhelming (karşı konulamaz) olarak tanımlıyor. Görünüşe göre maliyet, risk ve karmaşıklık artık potansiyel yararlardan daha ağır basıyor üzere görünüyor.

Intel’in patenti bir yalıtkan duvar vazifesi gören yeni, atom inceliğinde bir germanyum sinema ile eşleştirilmiş nanoşerit transistörlerin kullanımını ortaya koyuyor. Bu duvar, katmanlar ortasında fizikî bir ayraç vazifesi ve ayrıyeten p-gate kanalı ile n-geçitli kanal ortasında bir yalıtkan misyonu görüyor. Ayrıyeten birbiri üzerine kaç tane transistör istiflendiğine bağlı olarak dikey olarak istiflenmiş transistör katmanlarının her biri boyunca tekrarlanıyor.

Sonuç olarak teknoloji devi daha dar bir alana çok daha fazla transistör sığdırabilecek. Şirket teknolojiyi 2019’da keşfetmeye başlamıştı ve birinci olarak Elektronik Aygıtlar Toplantısı (IEDM) etkinliğinde bu gelişmeyi duyurdu. Maalesef patent ve teknolojiyle ilgili transistör yoğunluğu, performans ve güç verimliliği üzere hiçbir bahiste somut bilgiler bulunmuyor.

Tüm patentlerin her vakit zaman gerçek eserlere yahut üretim teknolojilerine dönüşmediğini hatırlatmakta yarar var. Fakat teknoloji dünyası er ya da geç 2nm ve altındaki teknolojilere muhtaçlık duyacak. Intel’in yanı sıra TSMC ve Samsung üzere dökümhaneler de kendi teknolojilerini geliştirmek için mesai harcıyor.

Intel 2nm’lik süreçte bu “stacked forksheet (yığınlanmış çatal levha)” mimarisinin yerine diğer teknikler de kullanabilir. Lakin şirket patent başvurusunu yaptı ve bu da nihayetinde dizaynın geçerliliği olduğu manasına geliyor.

Türkiye'nin en güncel forumlardan olan forumdas.com.tr'de forumda aktif ve katkısı olabilecek kişilerden gönüllü katkıda sağlayabilecek kişiler aranmaktadır.

Türkiye'nin en güncel forumlardan olan forumdas.com.tr'de forumda aktif ve katkısı olabilecek kişilerden gönüllü katkıda sağlayabilecek kişiler aranmaktadır.